- 您现在的位置:买卖IC网 > Sheet目录1998 > ICS874002AGLFT (IDT, Integrated Device Technology Inc)IC PCI EXPRSS/JITT ATTEN 20TSSOP

PCI EXPRESS/JITTER ATTENUATOR

ICS874002

IDT / ICS PCI EXPRESS/JITTER ATTENUATOR

1

ICS874002AG REV. A DECEMBER 6, 2006

GENERAL DESCRIPTION

The ICS874002 is a high performance Differential-

to-LVDS Jitter Attenuator designed for use in PCI

Express systems. In some PCI Express systems,

such as those found in desktop PCs, the PCI

Express clocks are generated from a low

bandwidth, high phase noise PLL frequency synthesizer. In

these systems, a jitter attenuator may be required to attenuate

high frequency random and deterministic jitter components

from the PLL synthesizer and from the system board. The

ICS874002 has 3 PLL bandwidth modes: 200kHz, 400kHz, and

800kHz. The 200kHz mode will provide maximum jitter

attenuation, but with higher PLL tracking skew and spread

spectrum modulation from the motherboard synthesizer may

be attenuated. The 400kHz provides an intermediate band-

width that can easily track triangular spread profiles, while

providing good jitter attenuation. The 800kHz bandwidth

provides the best tracking skew and will pass most spread

profiles, but the jitter attenuation will not be as good as the

lower bandwidth modes. Because some 2.5Gb serdes have x20

multipliers while others have than x25 multipliers, the

ICS874002 can be set for 1:1 mode or 5/4 multiplication mode

(i.e. 100MHz input/125MHz output) using the F_SEL pin.

The ICS874002 uses IDT’s 3rd Generation FemtoClockTM

PLL technology to achieve the lowest possible phase noise.

The device is packaged in a 20 Lead TSSOP package, making

it ideal for use in space constrained applications such as PCI

Express add-in cards.

FEATURES

Two differential LVDS output pair

One differential clock input

CLK and nCLK supports the following input types:

LVPECL, LVDS, LVHSTL, SSTL, HCSL

Output frequency range: 98MHz - 160MHz

Input frequency range: 98MHz - 128MHz

VCO range: 490MHz - 640MHz

Cycle-to-cycle jitter: 35ps (maximum)

3.3V operating supply

Three bandwidth modes allow the system designer to make

jitter attenuation/tracking skew design trade-offs

0°C to 70°C ambient operating temperature

Available in both standard (RoHS 5) and lead-free (RoHS 6)

packages

HiPerClockS

ICS

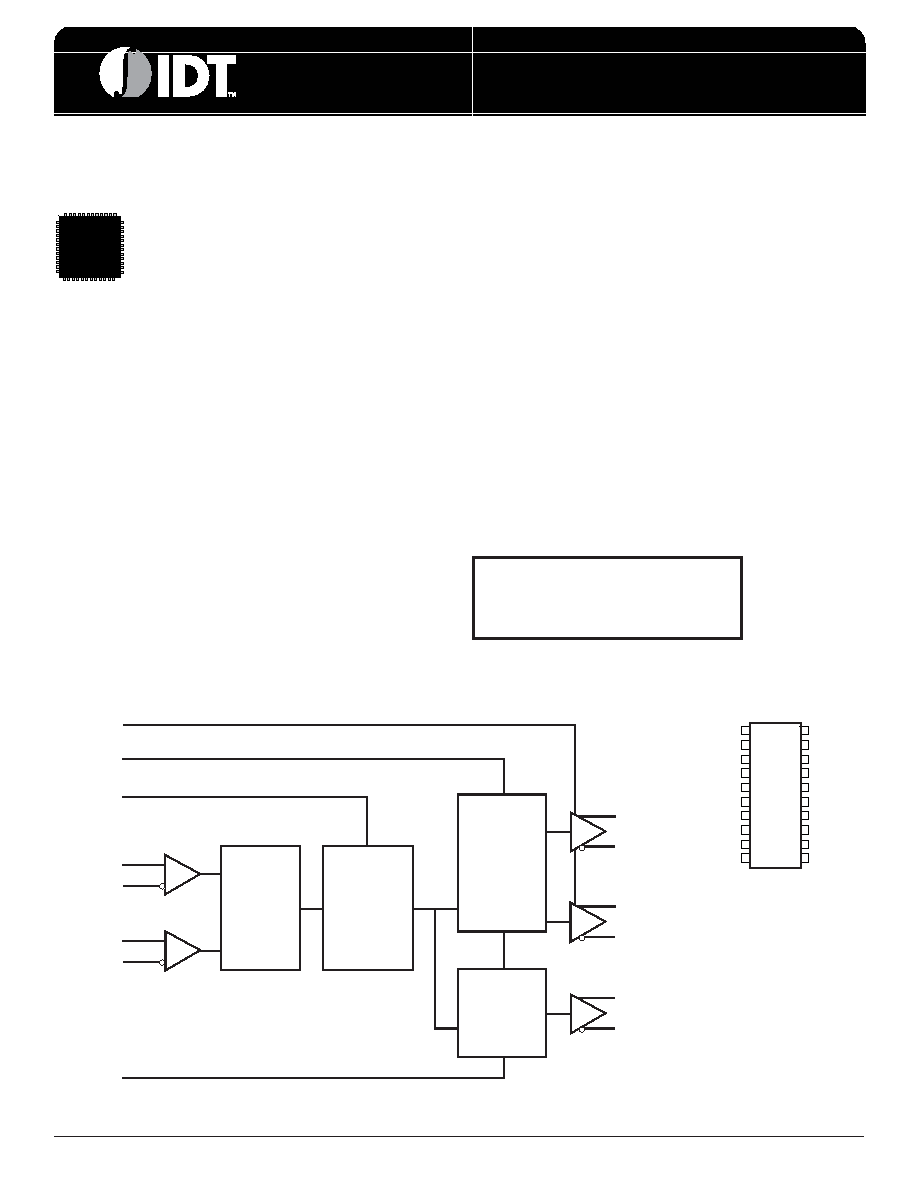

BLOCK DIAGRAM

BW_SEL

0 = PLL Bandwidth: 200kHz

Float = PLL Bandwidth: 400kHz (Default)

1 = PLL Bandwidth: 800kHz

PLL BANDWIDTH (TYPICAL)

÷5 (fixed)

VCO

490 - 640 MHz

Phase

Detector

Output Divider

0 ÷5 (default)

1 ÷4

QA0

nQA0

QA1

nQA1

FB_OUT

nFB_OUT

BW_SEL

0 = 200kHz

Float = 400kHz

1 = 800kHz

CLK

nCLK

FB_IN

nFB_IN

F_SEL

MR

OE

Float

Pulldown

Pullup

Pulldown

Pullup

Pulldown

PIN ASSIGNMENT

ICS874002

20-Lead TSSOP

6.5mm x 4.4mm x 0.92mm

package body

G Package

Top View

nQA0

VDDO

FB_OUT

nFB_OUT

MR

BW_SEL

nc

VDDA

F_SEL

VDD

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

QA0

VDDO

QA1

nQA1

nFB_IN

FB_IN

GND

nCLK

CLK

OE

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS874005AG-04LFT

IC PCI EXPRSS/JITT ATTEN 24TSSOP

ICS874005AGLFT

IC PCI EXPRSS/JITT ATTEN 24TSSOP

ICS8741004AGLFT

IC PCI EXPRSS/JITT ATTEN 24TSSOP

ICS87604AGILF

IC CLK MULT/ZD BUFFER 28-TSSOP

ICS8761CYLFT

IC CLK GEN PCI/PCI-X 64-LQFP

ICS87946AYILFT

IC CLOCK GENERATOR 32-LQFP

ICS87949AYILFT

IC CLOCK GEN LVCMOS 52-LQFP

ICS87950BYILF

IC CLK MULT LVCMOS/LVTTL 32-LQFP

相关代理商/技术参数

ICS874003AG-02LF

功能描述:IC JITTER ATTENUATOR 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

ICS874003AG-02LFT

功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS874003AG-04LF

功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS874003AG-04LFT

功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS874003AGI-02LF

功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

ICS874003AGI-02LFT

功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS874003AGLF

功能描述:IC JITTER ATTENUATOR 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

ICS874003AGLFT

功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT